History of Apple Computer Models

I have been an Apple programmer specializing in high-performance applications since the Apple II in 1980. My interest in processor performance is almost as old (see for example Super MANDELZOOM, my A005646 calculations, Sloandora and my Gray-Scott explorer). I continue to use my software from the 1980's and 1990's through emulators.

Details of Certain Specific Systems

Apple's Special Relationship With Intel

High-Level Design

Intel Product Cycle

Overview of Recent Intel Codenames

Chronology of Intel Silicon Fabrication Process Technology

Silicon Fabrication Advances

Intel's New Process Announcements

Chronology of Memory Products and Process Technology

Recent Memory Module Characteristics and Performance

PowerPC

Appendix B: Silicon Technology

Appendix D: The Detritus of Research

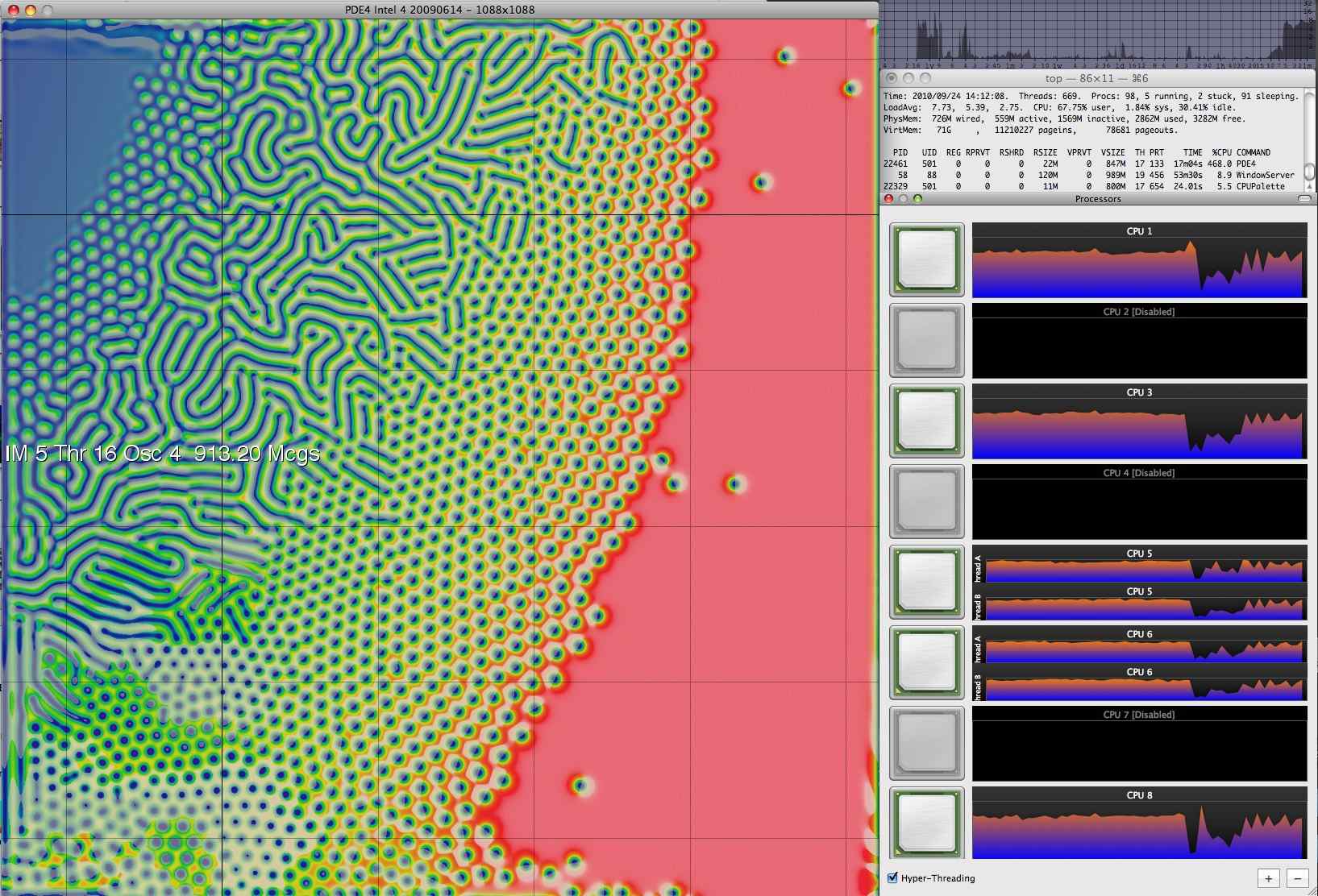

PDE4 on an 8-core Mac Pro with 5 cores and 7 threads enabled

I am continually looking for the next big chance to do more and better number-crunching, and I have written much on benchmarks (see for example my detailed work on how to compare all versions of the SPEC CPU Benchmarks).

This page was inspired by the Wikipedia page Timeline of Apple Macintosh models, and still draws from it heavily. I have added some non-Macintosh computers, made many of the dates more accurate, added details for recent models and an extensive section at the end that attempts to predict future developments.

| Year | Available | Model | Family | Announced2 | Discontinued | Details |

| 1976 | Apr | Apple 1 | Motherboard | 1976 April | 1977 | |

| 1977 | Jun 5 | Apple ][ | Desktop | 1977 Apr 16 | 1980 | |

| 1979 | Apple ][+4 | Desktop | 1979 | 1983 | ||

| 1980 | Jun | Apple /// | Desktop | 1980 May | 1985 | |

| 1983 | Jan | Lisa | All-In-One1 | 1983 Jan | 1985 Jan 1 | |

| Apple //e | Desktop | 1983 Jan | 1984 Jan | |||

| 1984 | Jan 24 | Lisa 2 | All-In-One1 | 1984 Jan 24 | 1985 Mar | |

| Apr? | Macintosh 128K4 | Compact AiO1 | 1984 Jan 24 | 1985 Jan 10 | ||

| Apr | Apple //c | Portable | 1984 Apr | |||

| Sep? | Macintosh 512K | Compact AiO1 | 1984 Sep 10 | 1986 Apr 14 | ||

| 1985 | Jan | Macintosh XL | Compact AiO1 | 1985 Jan 1 | 1986 Aug 1 | |

| Mar | Apple //e enhanced | Desktop | 1985 Mar | 1993 | ||

| 1986 | Jan | Macintosh Plus | Compact AiO1 | 1986 Jan 16 | 1990 Oct 15 | |

| Apr | Macintosh 512Ke4 | Compact AiO1 | 1986 Apr 14 | 1987 Oct 1 | ||

| Sep | Apple IIGS | Desktop | 1986 Jan 16 | 1992 Dec | ||

| 1987 | Mar | Macintosh SE | Compact AiO1 | 1987 Feb 3 | 1989 Aug 1 | |

| Mar | Macintosh II | Desktop | 1987 Mar 2 | 1990 Jan 15 | ||

| 1988 | Sep | Macintosh IIx | Desktop | 1988 Sep 19 | 1990 Oct 15 | |

| ? | Apple //c plus | Portable | 1988 Sep | 1990 Nov | ||

| 1989 | Jan 19 | Macintosh SE/30 | Compact AiO1 | 1989 Jan 19 | 1991 Oct 21 | |

| Mar 7 | Macintosh IIcx | Desktop | 1989 Mar 7 | 1991 Mar 11 | ||

| Aug 1 | Macintosh SE FDHD | Compact AiO1 | 1989 Aug 1 | 1990 Oct 15 | ||

| Sep 20 | Macintosh IIci | Desktop | 1989 Sep 20 | 1993 Feb 20 | ||

| Macintosh Portable | Portable | 1989 Sep 20 | 1991 Feb 11 | |||

| 1990 | Mar 19 | Macintosh IIfx | Desktop | 1990 Mar 19 | 1992 Apr 15 | |

| Oct 15 | Macintosh LC | Desktop | 1990 Oct 15 | 1992 Mar 23 | ||

| Macintosh Classic | Compact AiO1 | 1990 Oct 15 | 1992 Sep 14 | |||

| Macintosh IIsi4 | Desktop | 1990 Oct 15 | 1993 Mar 15 | |||

| 1991 | Feb 11 | Macintosh Portable (backlit screen) | Portable | 1991 Feb 11 | 1991 Oct 21 | |

| Oct 21 | Macintosh Classic II | Compact AiO1 | 1991 Oct 21 | 1993 Sep 13 | ||

| Quadra 700 | Desktop | 1991 Oct 21 | 1993 Mar 15 | |||

| Quadra 900 | Desktop | 1991 Oct 21 | 1992 May 18 | |||

| PowerBook 100 | Consumer Portable | 1991 Oct 21 | 1992 Aug 3 | |||

| PowerBook 1404 | Pro Portable | 1991 Oct 21 | 1992 Aug 3 | |||

| PowerBook 170 | Pro Portable | 1991 Oct 21 | 1992 Oct 19 | |||

| 1992 | Mar 23 | Macintosh LC II | Desktop | 1992 Mar 23 | 1993 Mar 15 | |

| May 18 | Quadra 950 | Desktop | 1992 May 18 | 1995 Oct 14 | ||

| Aug 3 | PowerBook 145 | Portable | 1992 Aug 3 | 1993 Jul 7 | ||

| Oct 19 | Macintosh IIvi | Desktop | 1992 Oct 19 | 1993 Feb 10 | ||

| Macintosh IIvx | Desktop | 1992 Oct 19 | 1993 Oct 10 | |||

| PowerBook 160 | Portable | 1992 Oct 19 | 1993 Aug 16 | |||

| PowerBook 180 | Portable | 1992 Oct 19 | 1994 May 16 | |||

| PowerBook Duo 210 | Portable | 1992 Oct 19 | 1993 Oct 21 | |||

| PowerBook Duo 230 | Portable | 1992 Oct 19 | 1994 Jul 27 | |||

| 1993 | Feb 10 | Macintosh LC III / III+ | Desktop | 1993 Feb 10 | 1994 Feb 14 | |

| Macintosh Color Classic | Compact AiO1 | 1993 Feb 10 | 1994 May 16 | |||

| Centris 610 | Desktop | 1993 Feb 10 | 1993 Oct 21 | |||

| Centris 650 | Desktop | 1993 Feb 10 | 1993 Oct 21 | |||

| Quadra 800 | Desktop | 1993 Feb 10 | 1994 Mar 14 | |||

| PowerBook 165c | Portable | 1993 Feb 10 | 1993 Dec 13 | |||

| Mar 22 | Workgroup Server 80 | Server | 1993 Mar 22 | 1995 Oct 17 | ||

| Workgroup Server 95 | Server | 1993 Mar 22 | 1995 Apr 3 | |||

| Jun 7 | PowerBook 145b | Portable | 1993 Jun 7 | 1994 Jul 18 | ||

| PowerBook 180c | Portable | 1993 Jun 7 | 1994 Mar 14 | |||

| Jun 28 | Macintosh LC 520 | Desktop | 1993 Jun 28 | 1994 Feb 2 | ||

| Jul 26 | Workgroup Server 60 | Server | 1993 Jul 26 | 1995 Oct 17 | ||

| Jul 29 | Centris / Quadra 660AV4 | Desktop | 1993 Jul 29 | 1994 Sep 12 | ||

| Quadra 840AV | Desktop | 1993 Jul 29 | 1994 Jul 18 | |||

| Aug 16 | PowerBook 165 | Portable | 1993 Aug 16 | 1994 Jul 18 | ||

| Oct 10 | Macintosh Color Classic II | Compact AiO1 | 1993 Oct 10 | 1995 Nov 1 | ||

| Oct 21 | Macintosh TV | Desktop | 1993 Oct 21 | 1995 Feb 1 | ||

| Quadra 605 | Desktop | 1993 Oct 21 | 1994 Oct 17 | |||

| Quadra 610 | Desktop | 1993 Oct 21 | 1994 Jul 18 | |||

| Quadra 650 | Desktop | 1993 Oct 21 | 1994 Sep 12 | |||

| PowerBook Duo 250 | Portable | 1993 Oct 21 | 1994 May 16 | |||

| PowerBook Duo 270c | Portable | 1993 Oct 21 | 1994 May 16 | |||

| 1994 | Feb 2 | Macintosh LC 550 | Desktop | 1994 Feb 2 | 1995 Mar 23 | |

| Macintosh LC 575 | Desktop | 1994 Feb 2 | 1995 Apr 3 | |||

| Mar 14 | Power Macintosh 61004 | Desktop | 1994 Mar 14 | 1996 May 18 | ||

| Power Macintosh 7100 | Desktop | 1994 Mar 14 | 1996 Jan 6 | |||

| Power Macintosh 8100 | Desktop | 1994 Mar 14 | 1996 Aug 14 | |||

| Apr 26 | Workgroup Server 6150 | Server | 1994 Apr 26 | 1995 Oct 1 | ||

| Workgroup Server 8150 | Server | 1994 Apr 26 | 1996 Feb 26 | |||

| Workgroup Server 9150 | Server | 1994 Apr 26 | 1996 Feb 26 | |||

| May 16 | PowerBook 520/c | Portable | 1994 May 16 | 1995 Sep 16 | ||

| PowerBook 540/c | Portable | 1994 May 16 | 1995 Aug 16 | |||

| PowerBook 550 | Portable | 1994 May 16 | 1996 Apr 1 | |||

| PowerBook Duo 280/c | Portable | 1994 May 16 | 1994 Nov 14 | |||

| Jul 18 | Quadra 630 | Desktop | 1994 Jul 18 | 1995 Apr 17 | ||

| PowerBook 150 | Portable | 1994 Jul 18 | 1995 Oct 14 | |||

| 1995 | Jan 28 | Power Macintosh 6200 / 6300 | Desktop | 1995 Jan 28 | 1996 Oct 17 | |

| Apr 3 | Macintosh LC 580 | Desktop | 1995 Apr 3 | 1995 Oct 1 | ||

| Performa 5200 | Desktop | 1995 Apr 3 | 1996 Oct 1 | |||

| Jun 19 | Power Macintosh 9500 | Desktop | 1995 Jun 19 | 1997 Feb 17 | ||

| Aug 7 | Power Macintosh 7200 | Desktop | 1995 Aug 7 | 1996 Apr 1 | ||

| Power Macintosh 7500 | Desktop | 1995 Aug 7 | 1997 Feb 17 | |||

| Power Macintosh 8500 | Desktop | 1995 Aug 7 | 1997 Feb 17 | |||

| Aug 28 | PowerBook 190 | Pro Portable | 1995 Aug 28 | 1996 Sep 1 | ||

| PowerBook 5300 | Portable | 1995 Aug 28 | 1996 Sep 1 | |||

| PowerBook Duo 2300c | Portable | 1995 Aug 28 | 1997 Feb 1 | |||

| 1996 | Feb 15 | Apple Network Server 500 | Server | 1996 Feb 15 | 1997 Apr 1 | |

| Apple Network Server 700/150 | Server | 1996 Feb 15 | 1997 Apr 1 | |||

| Feb 26 | Workgroup Server 7250 | Server | 1996 Feb 26 | 1997 Apr 21 | ||

| Workgroup Server 8550 | Server | 1996 Feb 26 | 1997 Apr 21 | |||

| Mar 10 | Performa 5260 / 5300 | Desktop | 1996 Mar 10 | 1997 Apr 1 | ||

| Apr 1 | Performa 5400 | Desktop | 1996 Apr 1 | 1997 Feb 17 | ||

| Power Macintosh 7600 | Desktop | 1996 Apr 1 | 1997 Oct 1 | |||

| Oct 16 | Apple Network Server 700/200 | Network Server | 1996 Oct 16 | 1997 Apr 1 | ||

| Oct 17 | Performa 6360 | Desktop | 1996 Oct 17 | 1997 Oct 1 | ||

| Oct 23 | Performa 6400 | Desktop | 1996 Oct 23 | 1997 May 1 | ||

| Nov 15 | Power Macintosh 4400 | Desktop | 1996 Nov 15 | 1997 Oct 11 | ||

| Nov 20 | PowerBook 1400 | Portable | 1996 Nov 20 | 1998 May 6 | ||

| 1997 | Feb 17 | Power Macintosh 5500 | Desktop | 1997 Feb 17 | 1998 Mar 31 | |

| Power Macintosh 6500 | Desktop | 1997 Feb 17 | 1998 Mar 14 | |||

| Power Macintosh 7300 | Desktop | 1997 Feb 17 | 1997 Nov 10 | |||

| Power Macintosh 8600 | Desktop | 1997 Feb 17 | 1998 Feb 17 | |||

| Power Macintosh 9600 | Desktop | 1997 Feb 17 | 1998 Mar 17 | |||

| PowerBook 3400 | Portable | 1997 Feb 17 | 1998 Mar 14 | |||

| Mar 19 | Twentieth Anniversary Macintosh | All-in-One1 | 1997 Mar 19 | 1998 Mar 14 | ||

| Mar 24 | Newton Messagepad 2000 | PDA3 | 1997 Mar 24 | ? | ||

| Apr? | eMate 300 | PDA3 | 1997 Jan 7 | |||

| Apr 21 | Workgroup Server 7350 | Server | 1997 Apr 21 | 1998 Mar 2 | ||

| Workgroup Server 9650 | Server | 1997 Apr 21 | 1998 Mar 2 | |||

| May 8 | PowerBook 2400c | Portable | 1997 May 8 | 1998 Mar 14 | ||

| Nov 10 | Power Macintosh G3 desktop | Pro Desktop | 1997 Nov 10 | 1999 Jan 5 | ||

| Power Macintosh G3 minitower | Pro Desktop | 1997 Nov 10 | 1999 Jan 5 | |||

| PowerBook G3 | Pro Portable | 1997 Nov 10 | 1998 Mar 14 | |||

| 1998 | Jan 31 | Power Macintosh G3 AIO | All-in-One1 | 1998 Jan 31 | 1998 Oct 17 | |

| Mar 2 | Macintosh Server G3 | Server | 1998 Mar 2 | 1999 Jan 1 | ||

| May 6 | PowerBook G3 series | Pro Portable | 1998 May 6 | 1999 May 10 | ||

| Aug 15 | iMac | Consumer Desktop | 1998 Aug 15 | 1999 May 10 | ||

| 1999 | Jan 5 | Power Mac G3 (Blue & White)4 | Pro Desktop | 1999 Oct 13 | details | |

| May 10 | PowerBook G3 ("Lombard") | Pro Portable | 2000 Feb 16 | |||

| Aug 31 | Power Mac G3 (450 MHz) | Pro Desktop | 2000 Xxx xx | details | ||

| Jul 21 | iBook | Consumer Port. | 2000 Sep 13 | |||

| Oct 5 | iMac (slot loading) | Consumer Desktop | 2002 Jan 7 | |||

| Oct 13 | Power Mac G4 Graphite | Pro Desktop | 2001 Jul 18 | |||

| 2000 | Feb 16 | PowerBook ("Pismo") | Pro Portable | 2001 Jan 9 | ||

| Power Mac G4 500 | Pro Desktop | details | ||||

| Jul 19 | Power Macintosh G4 Cube | Compact Desktop | 2001 Jul 3 | |||

| Sep 13 | iBook (FireWire) | Consumer Port. | 2001 May 1 | |||

| 2001 | Jan 9 | Power Mac G4 (Digital Audio) | Pro Desktop | 2001 Jul 18 | details | |

| Jan 31 | PowerBook G4 Titanium | Pro Portable | 2001 Jan 9 | 2003 Sep 16 | ||

| Feb 28 | Power Mac G4 (667 and 733) | Pro Desktop | 2001 Jan 9 | 2001 Jul 18 | details | |

| May 1 | iBook (white) | Consumer Port. | 2003 Oct | |||

| Jul 18 | Power Mac G4 Quicksilver | Pro Desktop | 2002 Jan 28 | details | ||

| 2002 | Jan 7 | iMac G4 15"4 | Consumer Desktop | 2004 Feb 4 | details | |

| Jan 28 | Power Mac G4 Quicksilver | Pro Desktop | 2002 Aug 13 | details | ||

| iBook (14") | Consumer Port. | 2003 Oct 22 | ||||

| Apr 29 | eMac | Consumer Desktop | sometime after 2006 Jul 3 | |||

| May 14 | Xserve | Rackmount Server | 2003 Feb 10 | |||

| Jul 17 | iMac G4 17"4 | Consumer Desktop | 2002 Jul 17 | 2003 Feb 4 | details | |

| Aug 13 | Power Macintosh G4 MDD | Pro Desktop | 2003 Jan 28 | details | ||

| 2003 | Jan 7 | PowerBook G4 Aluminum (12") | Pro Portable | 2006 May 16 | ||

| PowerBook G4 Aluminum (17") | Pro Portable | 2006 Apr 24 | ||||

| Jan 28 | Power Macintosh G4 (FW 800) | Pro Desktop | 2003 Jun 23 | details | ||

| Feb 4 | iMac G4 (X Only) | Consumer Desktop | 2003 Feb 4 | 2003 Sep 8 | details | |

| Feb 10 | Xserve slot loading | Rackmount Server | 2004 Jan 6 | |||

| Xserve Cluster Node | Rackmount Server | 2004 Jan 6 | ||||

| Jun 23 | Power Mac G5 | Pro Desktop | 2004 Jun 9 | details | ||

| Sep 9 | iMac G4 (USB 2.0) | Consumer Desktop | 2004 Jul 1 | details | ||

| Sep 16 | PowerBook G4 Aluminum (15") | Pro Portable | 2006 Feb 14 | |||

| Oct 22 | iBook G4 (12"/14")4 | Consumer Port. | 2006 May 16 | details | ||

| Nov 18 | iMac G4 20" | Consumer Desktop | 2004 Aug 31 | details | ||

| Power Mac G5 Dual 1.8 | Pro Desktop | 2004 Jun 9 | ||||

| 2004 | Jan 6 | Xserve G5 | Rackmount Server | 2006 Aug 7 | ||

| Xserve Cluster Node G5 | Rackmount Server | 2006 Aug 7 | ||||

| Jun 9 | Power Mac G5 (PCI-X 2)4 | Pro Desktop | 2005 Apr 27 | details | ||

| Aug 31 | iMac G5 | Consumer Desktop | 2005 May 3 | details | ||

| Oct 19 | Power Mac G5 Single | Pro Desktop | 2005 Apr 27 | details | ||

| 2005 | Jan 11 | Mac mini (original) | Compact Desktop | 2005 Sep 27 | details | |

| Apr 27 | Power Mac G5 | Pro Desktop | 2005 Oct 19 | details | ||

| May 3 | iMac G5 (ALS) | Consumer Desktop | 2005 Oct 12 | details | ||

| Sep 27 | Mac Mini (1.33/1.5) | Compact Desktop | details | |||

| Oct 12 | iMac G5 (iSight) | Consumer Desktop | 2006 Jan 10 | details | ||

| Oct 19 | Power Mac G5 Quad | Pro Desktop | 2006 Aug 7 | details | ||

| 2006 | Jan 10 | iMac Core Duo (17" / 20") | Consumer Desktop | 2006 Sep 6 | details | |

| never | MacBook Pro (15" 1.67 GHz) | Pro Portable | 2006 Jan 10 | 2006 Feb 14 | details | |

| Feb 14 | MacBook Pro (15") | Pro Portable | 2006 Jan 10 | 2008 Feb 26 | details | |

| Feb 28 | Mac mini (Intel Core Solo) | Compact Desktop | 2006 Sep 6 | details | ||

| Feb 28 | Mac mini (Intel Core Duo) | Compact Desktop | 2007 Aug 7 | details | ||

| Apr 24 | MacBook Pro (17") | Pro Portable | 2006 Oct 2x | details | ||

| May 16 | MacBook | Consumer Port. | 2006 Nov 0x | |||

| Aug 7 | Mac Pro (Woodcrest) | Pro Desktop | 2008 Jan 8 | details | ||

| Aug 7 | XServe (Intel) | Rackmount Server | 2008 Jan 8 | |||

| Sep 6 | Mac mini | Compact Desktop | details | |||

| Sep 6 | iMac | Consumer Desktop | 2007 Aug 7 | details | ||

| Oct 24 | MacBook Pro (Core 2 Duo)4 | Pro Portable | 2007 Jun 5 | details | ||

| Nov 0x | MacBook (Core 2 Duo) | Consumer Port. | 2008 Feb 26 | |||

| 2007 | Apr 4 | Mac Pro 8-core Clovertown | Pro Desktop | 2008 Jan 8 | details | |

| Jun 5 | MacBook Pro Santa Rosa | Pro Portable | 2008 Feb 26 | details | ||

| Jun 29 | iPhone (original) | PDA3 | 2007 Jan 9 | |||

| Aug 7 | iMac (aluminum enclosure) | Consumer Desktop | 2008 Apr 28 | details | ||

| Aug 7 | Mac mini (Core 2 Duo) | Compact Desktop | details | |||

| Nov 1 | MacBook Pro 2.6 GHz | Pro Portable | details | |||

| 2008 | Jan 8 | XServe Harpertown | Rackmount Server | |||

| Jan 8 | Mac Pro Harpertown | Pro Desktop | details | |||

| Jan 15 | MacBook Air | Consumer Port. | ||||

| Feb 26 | MacBook Penryn | Consumer Port. | ||||

| Feb 26 | MacBook Pro Penryn | Pro Portable | details | |||

| Apr 28 | iMac (Penryn) | Consumer Desktop | details | |||

| Jul 28 | iPhone 3G | PDA3 | 2008 Jun 9 | |||

| Oct 14 | MacBook Pro 15 (unibody) | details | ||||

| 2009 | Jan 6 | MacBook Pro 17 (unibody) | 2009 Jun 8 | details | ||

| Mar 3 | MacBook Pro 15 | 2009 Jun 8 | details | |||

| Mar 3 | Mac mini | Compact Desktop | details | |||

| Mar 3 | iMac (early 2009) | Consumer Desktop | details | |||

| Mar 3 | Mac Pro Nehalem4 | Pro Desktop | details | |||

| Jun 8 | MacBook Pro (SD card slot) | 2010 Apr 13 | details | |||

| Oct 20 | iMac (21.5 / 27) | Consumer Desktop | details | |||

| Oct 20 | Mac mini | Compact Desktop | details | |||

| Dec 4 | Mac Pro (late 2009) | Pro Desktop | details | |||

| 2010 | Apr 13 | MacBook Pro (mid 2010) | details | |||

| Jun 15 | Mac mini (unibody) | Compact Desktop | details | |||

| Jul 27 | iMac (ATI graphics) | Consumer Desktop | details | |||

| Aug 20 | Mac Pro Westmere | Pro Desktop | details | |||

| Oct 20 | MacBook Pro (2.8 option) | details | ||||

| 2011 | Feb 24 | MacBook Pro (Sandy Bridge)4 | details | |||

| May 3 | iMac Sandy Bridge | Consumer Desktop | details | |||

| 2012 | Jun 11 | Mac Pro "Meh" | Pro Desktop | details | ||

| Possible | Future Developments |

Details of Certain Specific Systems

These details are provided for the following purposes:

- To detail the specifications of the PCMS (processor, cache and memory system) which constitute most of the variation in system-level CPU benchmarks.

- Links to web pages for even more specs if you want it.

- Showing when the chip vendor (e.g. Intel) made the product available and their announced price. Future systems will probably be based on new CPUs with similar prices and with a similar delay after CPU release date. For portables and Mac Mini, wattage (TDP) is also a consderation. Using these criteria it is easy to predict that, for example, Apple will not use the first set of 6-core "Dunnington" processors because they cost too much (except possibly in XServe as a BTO for a new Cluster Node offering).

CPU: "G4" PowerPC 7447a at 1.25 GHz or 1.42 GHz

L2-Cache: 512K

Bus: 167 MHz

Memory: 333 MHz PC2700 DDR SDRAM

EveryMac profiles: 1.25 GHz, 1.42 GHz

CPU: "G4" PowerPC 7447a at 1.33 GHz or 1.5 GHz

L2-Cache: 512K

Bus: 167 MHz

Memory: 333 MHz PC2700 DDR SDRAM

EveryMac profiles: 1.33 GHz, 1.5 GHz

CPU: Intel "Yonah" Core Solo T1200 (1.5 GHz) or Core Duo T2300 (1.66 GHz)

L2-Cache: 2M

Bus: 667 MHz

Memory: 667 MHz PC2-5300 DDR2 SDRAM

CPU: "Yonah" Core Duo T2300 (1.66 GHz) or T2400 (1.83 GHz)

L2-Cache: 2M

Bus: 667 MHz

Memory: 667 MHz PC2-5300 DDR2 SDRAM

CPU: "Yonah" Core Duo T5600 (1.83 GHz) or T7200 (2.0 GHz)

L2-Cache: 2M

Bus: 667 MHz

Memory: 667 MHz PC2-5300 DDR2 SDRAM

CPU: "Penryn" Core 2 Duo P7350 (2.0 GHz) or P8400 (2.26 GHz)

L2-Cache: 3M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

CPU: "Penryn" Core 2 Duo P7550 (2.26 GHz), P8700 (2.53 GHz), or P8800 (2.66 GHz)

L2-Cache: 3M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

Mac Mini ("Unibody", June 2010)

CPU: "Penryn" Core 2 Duo P8600 (2.4 GHz) or P8800 (2.66 GHz)

L2-Cache: 3M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

iMac G4 (original with 15" screen), 2002 Jan 7 **

CPU: "G4" PowerPC 7441 at 700 MHz or 7445 at 800 MHz

L2-Cache: 256K

Bus: 100 MT/sec

Memory: PC133 SDRAM (133 MT/sec)

EveryMac profiles: 700 MHz, 800 MHz

iMac G4 (17" screen), 2002 Jul 17 **

CPU: "G4" PowerPC 7445 at 800 MHz

L2-Cache: 256K

Bus: 100 MT/sec

Memory: PC133 SDRAM (133 MT/sec)

CPU: "G4" PowerPC 7445 at 800 MHz or 1.0 GHz

L2-Cache: 256K

Bus: 100 or 133 MT/sec

Memory: PC133 (133 MT/sec) or PC2100 (266 MT/sec) SDRAM

EveryMac profiles: 800 MHz, 1.0 GHz

iMac G4 (USB 2), 2003 Sep 8 and Nov 18

CPU: "G4" PowerPC 7445 at 1.0 or 1.25 GHz

L2-Cache: 256K

Bus: 167 MT/sec

Memory: PC2700 (333 MT/sec) SDRAM

EveryMac profiles: 15" 1.0 GHz, 17" 1.25 GHz, 20" 1.25 GHz

CPU: "G5" PowerPC 970 at 1.6 or 1.8 GHz

L2-Cache: 512K

Bus: 533 or 600 MT/sec

Memory: PC3200 (400 MT/sec) SDRAM

EveryMac profiles: 17" 1.6 GHz, 17" 1.8 GHz, 20" 1.8 GHz

CPU: "G5" PowerPC 970 (or 970fx) at 1.8 or 2.0 GHz

L2-Cache: 512K

Bus: 600 or 667 MT/sec

Memory: PC3200 (400 MT/sec) SDRAM

EveryMac profiles: 17" 1.8 GHz, 17" 2.0 GHz, 20" 2.0 GHz

CPU: "G5" PowerPC 970fx at 1.9 or 2.1 GHz

L2-Cache: 512K

Bus: 633 or 700 MT/sec

Memory: PC2-4200 (533 MT/sec) DDR2 SDRAM

EveryMac profiles: 17" 1.9 GHz, 20" 2.1 GHz

iMac (17" and 20" core 2), 2006 Jan 10

CPU: "Yonah" Core Duo T2400 (1.83 GHz) or T2500 (2.0 GHz) (2006 Jan 5: $294 or $423)

L2-Cache: 2M (shared by both cores)

Bus: 667 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

EveryMac profiles: 17-inch, 20-inch

iMac (17", 20" and 24" core 2), 2006 Sep 6

CPU: "Merom" Core 2 Duo T7200 (2.0 GHz), T7400 (2.16 GHz) or T7600 (2.33 GHz) (2006 Aug 28: $294, $423, $637)

L2-Cache: 4M (shared by both cores)

Bus: 667 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

EveryMac profiles: 17" 2.0 GHz, 20" 2.16 GHz, 24" 2.33 GHz

There was also a model for education customers only, with a 1.83-GHz processor (Core 2 Duo T5600), and using Intel GMA 950 "integrated graphics". It was $899, but only for purchase by institutions (not even students or faculty). A profile is here.

CPU: "Merom" Core 2 Duo T7300 (2.0 GHz), T7700 (2.4 GHz) (2007 May 9: $241 or $530) or "Merom XE" Core 2 Extreme X7900 (2.8 GHz) (2007 Aug 22: $851)

L2-Cache: 4M (shared by both cores)

Bus: 800 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

EveryMac profiles: 20-inch 2.0 GHz, 24-inch 2.4 GHz, 24-inch 2.8 GHz

CPU: "Penryn" Core 2 Duo E8135 (2.4 GHz), O

E8335 (2.67 GHz), E8235 (2.8 GHz) or "Penryn XE" Core 2 Duo E8435 (3.06 GHz) (prices unknown)

L2-Cache: 6M (shared by both cores)

Bus: 1066 MT/sec (2.8 GHz model)

Memory: 800 MHz PC2-6400 DDR2 SDRAM

EveryMac profiles: 20-inch 2.4 GHz, [20-inch 2.67 GHz| [24-inch 2.8 GHz| 24-inch 3.06 GHz

CPU: "Penryn" Core 2 Duo E8135 (2.66 GHz), E8335 (2.93 GHz) or "Penryn XE" Core 2 Duo E8435 (3.06 GHz) (E8435 released 2008 Aug 10 at $266)

Cores/Threads: All models have 2 cores and 2 threads.

L2-Cache: 6M (shared by both cores)

Bus: 1066 MT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

EveryMac profiles: 20-inch 2.66 GHz, 24-inch 2.66 GHz, 24-inch 2.93 GHz, 24-inch 3.06 GHz

On April 7 Apple added a 20-inch, 2.0-GHz model for education customers only. A profile courtesy of EveryMac can be found here. Its price was $899, but individuals could not buy it, even if they were students or faculty — it could only be bought by institutions.

CPU: "Penryn XE" Core 2 Duo E8435 (3.06 GHz) or E8600 (3.33 GHz) or "Lynnfield" Core i5 750 (2.66-3.2 GHz) or Core i7 860 (2.8-3.46 GHz) (i5 and i7 both released 2009 Sep 8 at $196 and $284)

Cores/Threads: "Core 2 Duo" models have 2 cores and 2 threads; "Core i5" model has 4 cores and 4 threads; "Core i7" model has 4 cores and 8 threads.

L2-Cache: 3M (on E8435), 6M (on E8600) or 8M (on Core i5 and i7) (shared by all cores)

Bus: 1066 MT/sec (2.8 GHz model)

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

EveryMac profiles: 21.5-inch 3.06 GHz, 21.5-inch 3.33 GHz, 27-inch 3.06 GHz, 27-inch 3.33 GHz, 27-inch Core i5, 27-inch Core i7

iMac (ATI graphics), 2010 Jul 27

CPU: "Clarkdale" Core i3 540 (3.06 GHz dual-core) or 550 (3.2 GHz dual-core) or "Lynnfield" Core i5 760 (2.8-3.33 GHz quad-core) or "Clarkdale" Core i5 680 (3.6-3.86 GHz dual-core) or "Lynnfield" Core i7 875K (2.93-3.6 GHz quad-core)

Cores/Threads: all "dual-core" models have 2 cores and 4 threads; "Core i5 quad-core" model has 4 cores and 4 threads; "Core i7" model has 4 cores and 8 threads.

L2-Cache: 2M per core (i.e. 4M or 8M total)

Bus: 1333 MT/sec

Memory: 1.333 GHz PC3-10600 DDR3 SDRAM

EveryMac profiles: 21.5-inch 3.06 GHz Core i3, 21.5-inch 3.2 GHz Core i3, 21.5-inch 3.6 GHz Core i5, 27-inch 3.2 GHz Core i3, 27-inch 2.8 GHz Core i5, 27-inch 3.6 GHz Core i5, 27-inch 2.93 GHz Core i7

iMac (Sandy Bridge), 2011 May 3

CPU: "Sandy Bridge" Core i5 2400S (2.5-3.3 GHz), 2500S (2.7-3.7 GHz) or 2400 (3.1-3.4 GHz) or "Sandy Bridge" Core i7 2600S (2.8-3.8 GHz) or 2600 (3.4-3.8 GHz)

Cores/Threads: all "Core i5" models have 4 cores and 4 threads; "Core i7" models have 4 cores and 8 threads.

L2-Cache: 6M (Core i5) or 8M (Core i7)

Bus: 5 GT/s

Memory: 1.333 GHz PC3-10600 DDR3 SDRAM

EveryMac profiles: 21.5-inch 2.5 GHz Core i5 21.5-inch 2.7 GHz Core i5 21.5-inch 2.8 GHz Core i7 27-inch 2.7 GHz Core i5 27-inch 3.1 GHz Core i5 27-inch 3.4 GHz Core i7

(This model was made available only to educational customers.)

CPU: "Sandy Bridge" Core i3 2100 (3.1 GHz, no turbo boost)

Cores/Threads: 2 cores and 4 threads

L2-Cache: 3M

Bus: 5 GT/s

Memory: 1.333 GHz PC3-10600 DDR3 SDRAM

EveryMac profiles: 21.5-inch 3.1 GHz Core i3

Details for iBook and MacBook

This was a new line created in 1999 as a consumer-oriented portable. It initially had a substantially different look and feel from the PowerBooks, but has gradually converged over the following 10 years.

CPU: "G4" PowerPC 7457 at 800 MHz (12" model) or 933 MHz (14" model)

L2-Cache: 256K

Bus: 133 MT/sec

Memory: PC2100 DDR SDRAM (267 MT/sec)

Details for Powerbook and MacBook Pro

The never-shipped 1.67 GHz MacBook Pro 15"

CPU: "Yonah" Core Duo L2400 (1.67 GHz) (2006 Jan 5: $316)

L2-Cache: 2M (shared by both cores)

Bus: 667 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SO-DIMM

This system never shipped. On 2006 Feb 14, Apple announced that the MacBook Pro line (which had not yet shipped) would feature 1.83, 2.0 and 2.16 GHz processors, thus eliminating the 1.67 GHz version.

MacBook Pro, 2006 Feb 14 and 2006 Apr 24

CPU: "Yonah" Core Duo T2400 (1.83 GHz), T2500 (2.0 GHz) or T2600 (2.16 GHz) (2006 Jan 5: $294 - $637)

L2-Cache: 2M (shared by both cores)

Bus: 667 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SO-DIMM

lowendmac profiles: 15-inch, 17-inch

CPU: "Merom" Core 2 Duo T7400 (2.16 GHz) or T7600 (2.33 GHz) (2006 Aug 28: $423, $637)

L2-Cache: 4M (shared by both cores)

Bus: 667 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

EveryMac's profiles: 2.16 15", 2.33 17"

lowendmac profiles: 15-inch, 17-inch

MacBook Pro (Santa Rosa), 2007 Jun 5

CPU: "Merom" Core 2 Duo T7500 (2.2 GHz) or T7700 (2.4 GHz) (2007 May 9: $316, $530)

L2-Cache: 4M (shared by both cores)

Bus: 800 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

lowendmac profiles: 15-inch 17-inch

EveryMac's profiles: 2.2 15'', 2.4 17''

MacBook Pro (17'' 2.6 GHz option), 2007 Nov 1

CPU: "Merom" Core 2 Duo T7800 (2.6 GHz) (2007 Sep 2: $530)

L2-Cache: 4M (shared by both cores)

Bus: 800 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

EveryMac's profile (which only makes brief mention of the 2.6 GHz version)

MacBook Pro (Penryn), 2008 Feb 26 (2.5 and 2.6 GHz versions)

CPU: "Penryn" Core 2 Duo T8300 (2.4 GHz) or T9300 (2.5 GHz) or T9500 (2.6 GHz) (2008 Jan 6: $241, $316, $530)

L2-Cache: 3M (2.4 GHz models) or 6M (faster models) (shared by both cores)

Bus: 800 MT/sec

Memory: 667 MHz PC2-5300 DDR2 SDRAM

lowendmac profiles: 15-inch 17-inch

EveryMac's profiles: 2.4 15'' 2.5 15'', 2.6 17'' (which mentions the 2.6 GHz option)

MacBook Pro 15'' (Unibody), 2008 Oct 14

CPU: "Penryn" Core 2 Duo P8600 (2.4 GHz) (2008 Jun 13: $241), T9400 (2.533 GHz) or T9600 (2.8 GHz) (both 2008 Jul 14: $316, $530)

L2-Cache: 3M (2.4 model) or 6M (higher models) (cache is shared by both cores)

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC2-8500 DDR2 SDRAM

lowendmac profiles: 15-inch

NOTE: In 2008 Oct, the 17-inch MacBook Pro still had the same CPU, bus and memory specs as the 2008 Feb 26 version, but its screen and hard drive were changed in conjunction with the all-new "unibody" 15'' model.

MacBook Pro (17-inch Unibody, January 2009)

CPU: "Penryn" Core 2 Duo T9550 (2.66 GHz) or T9800 (2.93 GHz) ()

L2-Cache: 6M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC2-8500 DDR2 SDRAM

lowendmac profiles: 17-inch

EveryMac's profile: 2.66 17''

MacBook Pro (15-inch Unibody, March 2009)

CPU: "Penryn" Core 2 Duo T9550 (2.66 GHz) ()

L2-Cache: 6M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC2-8500 DDR2 SDRAM

EveryMac's profile: 2.66 15''

MacBook Pro (SD card slot, June 2009)

CPU: "Penryn" Core 2 Duo P8400 (2.26 GHz), P8700 (2.53 GHz), P8800 (2.66 GHz), T9600 (2.8 GHz), or T9900 (3.06 GHz) (20080714: $209 - $530)

Cores/Threads: All models have 2 cores and 2 threads.

L2-Cache: 3M (2.26, 2.53 and 2.66 GHz models) or 6M (2.8 and 3.06 GHz models)

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC2-8500 DDR2 SDRAM

lowendmac profiles: 13-inch 15-inch 17-inch

EveryMac's profiles: 2.26 13'' 2.53 13'' 2.53 15'' 2.66 15'' 2.8 15'' 2.8 and 3.06 17''

CPU: "Penryn" Core 2 Duo P8600 (2.4 GHz) or P8800 (2.66 GHz) (20080613: $241)

or "Arrandale" Core i5 520M (2.4-2.93 GHz) or 540M (2.53-3.06 GHz) (20100107: $225, $257)

or "Arrandale" Core i7 620M (2.66-3.33 GHz) (20100107: $332)

Cores/Threads: All models have 2 cores; "Core 2 Duo" models have 2 threads; "Core i5" and "Core i7" models have 4 threads.

L2-Cache: 3M (Core 2 Duo and Core i5 models) or 4M (2.66 Core i7 model)

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

EveryMac's profiles: 2.4 13'' 2.66 13'' 2.4 15'' 2.53 15'' 2.66 15'' 2.53 and 2.66 17''

MacBook Pro (2.8 GHz option), Oct 2010

CPU: "Arrandale" Core i7 640M (2.8-3.46 GHz) (20100926: $346)

Cores/Threads: 2 cores/4 threads.

L2-Cache: 4M

Bus: 1.066 GT/sec

Memory: 1.066 GHz PC3-8500 DDR3 SDRAM

CPU: 13'' models have "Sandy Bridge" Core i5 2410M (2.3-2.9 GHz), or Core i7 2620M (2.7-3.4 GHz) (20110221: $225, $346)

15'' and 17'' models have "Sandy Bridge" Core i7 2630QM (2.0-2.9 GHz), 2720QM (2.2-3.3 GHz) or 2820QM (2.3-3.4 GHz) (20110221: $378, $378, $568)

Cores/Threads: 13'' models have 2 cores and 4 threads; 15'' and 17'' models have 4 cores and 8 threads

L3-Cache: 3MB (13'' with Core i5), 4MB (13'' with Core i7), 6MB (2.0 GHz and 2.2 GHz quad-core), or 8MB (2.3 GHz quad-core)

Bus: 1.333 GT/sec

Memory: 1.333 GHz DDR3 SDRAM

lowendmac profiles: 13-inch 15-inch 17-inch

Idle Speculations on MacBook Pro

(none at present)

Details for PowerMac and Mac Pro

Power Mac G3 (Blue and White), 1999 Jan 5

CPU: IBM PowerPC 750 (300, 350 or 400 MHz)

L2-Cache: 512K (300 MHz model) or 1M (faster models)

Bus: 100 MHz

Memory: PC100 SDRAM

CPU: IBM PowerPC 750 (450 MHz)

L2-Cache: 1M

Bus: 100 MHz

Memory: PC100 SDRAM

Power Mac G4 "Gigabit Ethernet", 2000 Feb 16

CPU: 2x IBM PowerPC 750 (450 or 500 MHz)

L2-Cache: 2M (1M per processor)

Bus: 100 MHz

Memory: PC100 SDRAM

Power Mac G4 "Digital Audio", 2001 Jan 9

CPU: Motorola 7410 "Nitro" (single 466 MHz or dual 533 MHz)

L2-Cache: 1M (or 2M for dual 533 model)

Bus: 133 MHz

Memory: PC133 SDRAM

Power Mac G4 "Digital Audio", 2001 Feb

CPU: Motorola 7450 "V'ger" (667 or 733 MHz)

L2-Cache: 1M

Bus: 133 MHz

Memory: PC133 SDRAM

Power Mac G4 "Quicksilver", 2001 Jul 18

CPU: Motorola 7450 "V'ger" (733 or 867 MHz)

CPU: 2x Motorola 7450 "V'ger" (800 MHz)

L2-Cache: 1M (2M for dual 800 model)

Bus: 133 MHz

Memory: PC133 SDRAM

EveryMac profiles: 733, 867, dual 800

Power Mac G4 "Quicksilver", 2002 Jan 28

CPU: Motorola 7455 "Apollo 6" (800 or 933 MHz)

CPU: 2x Motorola 7455 "Apollo 6" (1.0 GHz)

L2-Cache: none on 800 MHz model; 2M on 933 MHz model; 4M (2M per processor) on 1.0 GHz model

Bus: 133 MHz

Memory: PC133 SDRAM

EveryMac profiles: 800, 933, dual 1.0

Power Mac G4 (Mirror Drive Doors), 2002 Aug 13

CPU: 2x Motorola 7455 "Apollo 6" (867 MHz, 1.0 GHz or 1.25 GHz)

L2-Cache: 1M (867 and 1.0 GHz models) or 2M (1.25 GHz model)

Bus: 133 MHz (867 model), 167 MHz (faster models)

Memory: 266 MHz PC2100 DDR SDRAM (867 model) or 333 MHz PC2700 DDR SDRAM (faster models)

EveryMac profiles: 867, 1.0, 1.25

Power Mac G4 (Firewire 800), 2003 Jan 28

CPU: Motorola 7455 "Apollo 6" (single 1.0 GHz, dual 1.25 or dual 1.42 GHz)

L2-Cache: 1M (1.0 GHz model), 2M (dual 1.25 GHz model), or 4M (dual 1.42 GHz model)

Bus: 133 MHz (1.0 GHz model), 167 MHz (faster models)

Memory: 266 MHz PC2100 DDR SDRAM (1.0 GHz model) or 333 MHz PC2700 DDR SDRAM (faster models)

EveryMac profiles: 1.0, 1.25, 1.42

CPU: IBM PowerPC 970 (single 1.6, single 1.8, or dual 2.0 GHz)

L2-Cache: 512K

Bus: 800 MHz, 900 Mhz or 1.0 GHz

Memory: 333 MHz PC2700 DDR RAM (1.6 GHz model) or 400 MHz PC3200 DDR RAM (faster models)

EveryMac profiles: 1.6, 1.8, 2.0

PowerMac G5 (PCI-X 2), 2004 Jun 9 **

CPU: 2x IBM PowerPC 970fx (1.8, 2.0 or 2.5 GHz)

L2-Cache: 1M (512K per CPU)

Bus: 900 Mhz, 1.0 GHz or 1.25 GHz

Memory: 400 MHz PC3200 DDR RAM

EveryMac profiles: 1.8, 2.0, 2.5

PowerMac G5 Single, 2004 Oct 19

CPU: IBM PowerPC 970fx (1.8 GHz)

L2-Cache: 512K

Bus: 600 Mhz

Memory: 400 MHz PC3200 RAM

CPU: 2x IBM PowerPC 970fx (2.0, 2.3 or 2.7 GHz)

L2-Cache: 1M (512K per CPU)

Bus: 1.0, 1.15 or 1.35 GHz

Memory: 400 MHz PC3200 DDR RAM

EveryMac profiles: 2.0, 2.3, 2.7

CPU: IBM PowerPC 970MP "Antares" (2.0 or 2.3 GHz)

L2-Cache: 2M (1M per core)

Bus: 1.0 or 1.15 GHz

Memory: 533 MHz PC2-4200 DDR2

CPU: 2x IBM PowerPC 970MP "Antares" (2.5 GHz)

L2-Cache: 4M (1M per core)

Bus: 1.25 GHz

Memory: 533 MHz PC2-4200 DDR2

CPU: 2x Intel Core 2 Duo "Woodcrest" 5130 (2.0 GHz), 5150 (2.66 GHz) or 5160 (3.0 GHz) (all 2006 Jun 26: $316 - $851)

L2-Cache: 8M (4M for each pair of cores)

Bus: 1.33 GT/sec

Memory: 667 MHz PC2-5300 DDR2 fully buffered (FB-DIMM) ECC RAM, dual channel (10.7 GB/s bandwidth)

CPU: 2x Intel Core 2 Quad "Clovertown" X5365 (3.0 GHz) (2007 April 4: $1350)

L2-Cache: 16M (each pair of cores shares 4M)

Bus: 1.33 GT/sec

Memory: 667 MHz PC2-5300 DDR2 fully buffered (FB-DIMM) ECC RAM, dual channel (10.7 GB/s bandwidth)

CPU: 2x Intel Core 2 Quad "Harpertown" E5462 (2.8 GHz), E5472 (3.0 GHz) or X5482 (3.2 GHz) (all 2007 Nov 11: $797 or 851, $958, $1279)

Cores/Threads: All models have 8 cores and 8 threads.

L2-Cache: 24M (each pair of cores shares 6M)

Bus: 1.6 GT/sec

Memory: 800MHz DDR2 ECC fully buffered DIMM (FB-DIMM) RAM, dual channel (12.8 GB/s bandwidth)

Mac Pro "Gainestown Nehalem", 2009 Mar 3 **

CPU: 1x Xeon W3520 (2.66 GHz) or W3540 (2.93 GHz) ($284, $562)

or 2x Xeon E5520 (2.26 GHz), X5550 (2.66 GHz) or X5570 (2.93 GHz) ($373 - $1386)

Cores/Threads: Each Xeon CPU has 4 cores and 8 threads; thus the dual-CPU machines have 8 cores and 16 threads.

Cache: 256K L2 and 2M L3 per core (1 processor = 4 cores, i.e. either 9M or 18M total cache)

Bus: Controls memory directly; uses QuickPath Interconnect at 5.86 GT/sec (2.26 GHz 8-core model) or 6.4 GT/sec (all other models) for data transfer between one processor and the other, and between processor(s) and the video, hard drives and rest of the system.

Memory: 1066 MHz DDR3 ECC SDRAM, triple channel (25.6 GB/s bandwidth per CPU socket)

EveryMac profiles: Quad 2.66, Octo-core 2.26.

Mac Pro (late 2009 3.33 GHz), 2009 Dec 4

CPU: 1x Xeon X5590 (3.33 GHz) ($1600)

Cores/Threads: 4 physical cores, 8 threads.

Cache: 256K L2 and 2M L3 per core (1 processor = 4 cores, i.e. 9M total cache)

Bus: Controls memory directly; uses QuickPath Interconnect at 6.4 GT/sec for data transfer between one processor and the other, and between processor(s) and the video, hard drives and rest of the system.

Memory: 1066 MHz DDR3 ECC SDRAM, triple channel (25.6 GB/s bandwidth)

Mac Pro "Westmere", 2010 August

CPU: 1x Xeon W3530 (2.8 GHz 4-core), W3565 (3.2 GHz 4-core) or W3680 (3.33 GHz 6-core) ($unknown, $562, $999)

or 2x Xeon E5620 (2.4 GHz 4-core), X5650 (2.66 GHz 6-core) or X5670 (2.93 GHz 6-core) ($387, $996, $1440)

Cores/Threads: From 4 to 12 cores, with 2 threads per core.

Cache: most models have 256K L2 and 2M L3 per core (i.e. from 9M to 27M total cache); the 8-core (2x Xeon E5620) model has 256K L2 and 3M L3 cache per core (26M total cache).

Bus: Controls memory directly; uses QuickPath Interconnect at 4.8 GT/sec (2.8 GHz 4-core model), 5.86 GT/sec (2x 2.4 GHz 4-core) or 6.4 GT/sec (6-core and 12-core models) for data transfer between one processor and the other, and between processor(s) and the video, hard drives and rest of the system.

Memory: 1066 MHz DDR3 ECC SDRAM (4-core and 6-core systems)

or 1333 MHz DDR3 ECC SDRAM (8-core and 12-core systems)

triple channel (25.6 GB/s or 32 GB/s bandwidth per CPU socket)

(After nearly two years, Apple updated its Mac Pro lineup ever so slightly: the 4-core entry system went from 2.8 GHz to 3.2 GHz (still $2500), and the top 12-core model went from 2.93 GHz up to 3.06 GHz (still $6200). Here is a news story about the 2012 changes: Apple incrementally updates Mac Pro desktop for 2012)

CPU: 1x Xeon W3565 (3.2 GHz 4-core) or W3680 (3.33 GHz 6-core) ($562, $999) or 2x Xeon E5645 (2.4 GHz 6-core), X5650 (2.66 GHz 6-core) or X5675 (3.06 GHz 6-core) ($551, $996, $1440) All other specs are the same as above. Note there is no longer an 8-core model.

Mac Pro "Ivy Bridge", 2013 Dec 19

CPU: 1x Xeon E5-1620v2 (3.7-3.9 GHz) or E5-1650v2 (3.5-3.9 GHz)

or E5-1680v2 (3.0-3.9 GHz) or E5-2697v2 (2.7-3.5 GHz)

($294 - $2614)

Cores/Threads: 4, 6, 8 or 12 cores, number of threads is twice as much

Cache: 256K L2 per core; 10M, 12M, 25M or 30M of L3 cache.

Bus: None (Controls memory and PCI directly)

Memory: DDR3-1866 (PC3-15000) ECC SDRAM, quad channel (total bandwidth 59.7 GB/s)

EveryMac profiles: 4-core 6-core 8-core 12-core

Idle Speculations for Mac Pro

The Situation in 2012 (speculation)

(written in 2012 June)

Lately there has been a lot of speculation that Apple would soon drop the Pro line entirely. Apple answered these doubts by making small changes to the CPU speeds of the lowest and highest Mac Pro models, while keeping the price structure the same. The fastest 12-core option uses the Xeon X5675, which Intel released in February 2011. Although it was released after the desktop Sandy Bridge processors, the Xeon X5675 is still a Westmere chip.

Intel has (in late 2011) updated its Xeon line to include Sandy Bridge, but the new Sandy Bridge Xeons provide no integrated Thunderbolt or USB 3.0 capability. This effectively makes it impossible for Apple to bring these upgrades (present on the MacBook Pro since the 2011 March models) to the Xeon-based Mac Pro.

Dual-Socket Workstations Similar to Mac Pro

This chart summarizes dates, prices, and performance figures for two-socket servers or workatations using the same Intel processors as Apple has used in most of its "middle-priced" Mac Pro. In each case:

- I chose processors identical to what Apple offered in Mac Pros (as seen above) extending forward to Sandy Bridge-EP to show what might have been possible if Apple had chosen to use those processors.

- I tried to choose processors that cost about $1000 each

- The date given is the date of the first SPEC benchmark result for a system with the given processor configuration

- The SPEC benchmark figures are weighted averages of all of the SPEC results for workstations and servers with two of the indicated Xeon processors

|

Apple's Special Relationship With Intel

On several occasions it has been clear that Apple has been able to get certain part numbers from Intel a little ahead of the rest of the industry. Recent examples include:

- 2007 Jan: The Pentium M "Crofton" used in Apple TV (see macnn [24]).

- 2007 Apr 4: The 3.0 GHz Xeon X5365 "Clovertown" used in the first 8-core Mac Pro (see electronista [25]).

- 2008 Apr 29: The 3.07 GHz Core 2 Extreme X9100 "Penryn", used in the top-model iMac months before being released to the general market on July 14. (see TG Daily [33]).

- 2008 Jan: The original MacBook Air's 1.6 and 1.8 GHz processors (described by Anand: [29] and [30]).

- 2009 Mar 3: The first Nehalem-based Mac Pros, using Xeon processors (the W3520, W3540, E5520, X5550 and X5570 or (by some accounts) X5580) about 3 weeks before being available to the general market (see TG Daily [55]).

Before Apple became a major customer of Intel, a similar type of relationship existed with IBM regarding the PowerPC G5 (the 970, 970FX, and 970MP).

In May 2011, a special Apple-Intel relationship was confirmed directly [90] by Intel's Tom Kilroy, who stated:

"We work very closely with them and we're constantly looking down the road at what we can be doing relative to future products. I'd go as far as to say Apple helps shape our roadmap"

More recently, Apple has been cited[107] as the reason for Intel adding much better integrated graphics (branded "HD Graphics 3000") to its mobile Sandy Bridge (2nd-Generation Core) processors, and similar even better-performing graphics to subsequent products, culminating with the 128 MiB eDRAM cache for the 4-core variants of Haswell with "Iris Pro 5200 Graphics", which were used in the late 2013 refresh of the 15-inch Retina MacBook Pro.

Appendix A: Charts and Tables

Charts and Tables of Intel-CPU-Specific History

Tick Tock Chart

This chart illustrates the general pattern of alternation between the development of semiconductor processes (see the lithography table below) and changes in computer architecture, illustrated by the past 20 years of Intel CPU history. Though Intel attached the "Tick-Tock" marketing to it in 2007, the practice (motivated mainly by risk-reduction and yield-based economics) is common throughout the industry and began long before Intel made it "a thing".

The cadence of new semiconductor fabrication processes is the most regular; the chart attempts to show the very first product for each new process, with source references in most cases.

For each new process, one representative microarchitecture change (or sometimes two) is shown.

| Generation | fab. | 4+ socket Server | 2-socket Workstation | High-end | Desktop | Mobile | First representative product | Apple example |

| microarch.: | 1 uM | - | - | |||||

| new process | 0.8 uM | - | - | 1991 Jun 24 (80486 50 MHz, see [10]) | ||||

| microarch.: | 0.8 uM | - | - | |||||

| new process | 0.6 uM | - | - | 1994 Mar 7 (80486 DX4 75 MHz, see [8] and [10]) | ||||

| microarch.: | 0.6 uM | - | - | |||||

| new process | 0.35 uM | - | - | 1995 Mar 27 (Pentium 133 MHz, from [8]) | ||||

| microarch.: | 350 | - | - | |||||

| new process | 0.25 uM | - | - | Deschutes | 1997 Sep 8 (mobile Pentium MMX 200,233 MHz, see [9]) | |||

| microarch.: | 250 | - | - | Katmai | ||||

| new process | 0.180 uM | - | - | Coppermine | Coppermine | 1999 Jun 14 (low volume production of the 400 MHz Mobile Pentium II, see [11]) 1999 Oct 25 (Pentium III, see [13]) | iMac G4 (early 2002) | |

| microarch.: Coppermine | 180 | Willamette | - | - | Willamette | Coppermine | 2000 Nov 20 (Pentium 4 1.4 and 1.5 GHz using Socket 423) | |

| new process | 0.130 uM | Northwood | - | - | Northwood | Tualatin | 2001 Jul 30 (mobile Pentium III 1.13 GHz, see [17]; sampled in May[16]) | iBook G4 (fall 2003) |

| microarch.: hyperthreading | 130 nm | - | - | Northwood | Banias | 2002 Nov 14 (Pentium 4 3.06GHz) | ||

| new process | 90nm | - | - | Prescott | Dothan | 2004 Feb 1 (Pentium 4 2.80 GHz, Pentium 4 HT 2.8E and 3.0E, see [19]) | PowerMac G5 (PCI-X 2) | |

| microarch.: | 90 | Irwindale (Skt 604) | Smithfield (LGA-775) | Prescott 2M (LGA-775) | Dothan | 2005 Feb | ||

| new process (and Pentium-M) | 65nm | Tulsa (Skt 604) | Dempsey (LGA-771) | Presler | Cedar Mill | Yonah | 2006 Jan 5 (Core Solo T1300 and several Core Duos) | |

| microarch.: Core 2 | 65 | Tigerton | Woodcrest/

Clovertown | Kentsfield | Conroe | Merom | 2006 Jul 27 (Core 2 Duo E6300-E6700) | MacBook Pro (October 2006) |

| new process | 45nm | Dunnington | Harpertown | Yorkfield | Wolfdale | Penryn | 2007 Nov 12 (Core 2 Extreme QX9650 and 12 Xeon 54xx models) and several Xeon models, see [27]) | |

| microarch.: Nehalem | 45 | Beckton (LGA-1567) | Gainestown (LGA-1366) | Bloomfield (LGA-1366) | Lynnfield (LGA-1156) | Clarksfield | 2008 Nov 17 (Core i7-920, i7-940 and i7-965) | Mac Pro (early 2009) |

| new process | 32nm | Westmere-EX | Westmere-EP | Gulftown | Clarkdale | Arrandale | 2010 Jan 7 | |

| microarch.: Sandy Bridge | 32 | (none) | Jaketown (Sandy Bridge-EP),

Sandy Bridge-EN (LGA-1356) | Sandy Bridge-E (LGA-2011) | Sandy Bridge (LGA-1155) | Sandy Bridge-M | 2011 Jan 9 (Core i7-2630QM through 2820QM) | MacBook Pro (early 2011) |

| new process | 22nm | Ivy Bridge-EX | Ivy Bridge-EP | Ivy Bridge | Ivy Bridge | 2012 Apr 23 (both desktop and mobile) | ||

| microarch.: Haswell | 22 | Haswell-DT | Haswell-MB, Haswell-LP | 2013 Jun 2 |

The main driving force behind these alternating cycles is the learning curve of process technology, and in particular the improvements in yield related to declining defect rate.

Because of initial low yields, a new process will be used only for products that:

- have smaller transistor counts (small die size)

- can be configured during burn-in by disabling defective sections and still be sellable, and/or

- can be sold for a high price

Any combination of these factors, together with market factors in the different product segments (embedded, mobile, desktop, server, etc.) can determine which market segment will get the new fab technology first. The third criterion (selling for a higher price) often drives this decision, and higher price is usually justified because of the benefits that smaller-scale fabrication provides:

- same performance with lower power consumption (ideal for mobile and server markets), or

- greater performance within any given power/heat limits by being able to run at a higher speed (an important driving force up until the "4 GHz wall" changed everything in 2004-2006) or by running at full speed a greater percentage of the time.

Whenever a given process reaches the point where yields are competitive with the previous (larger) process on a transistor count basis, it is possible to move existing products to the new process. This is a process shrink, and it happens at a point that is planned well in advance and timed to address market factors. As just mentioned, the process shrink allows for better power consumption and/or greater speed. As the yield learning curve continues to improve, the new process allows for cheaper manufacturing cost as well (because the product now fits on a physically smaller die).

As fabrication yields continue to improve, the new fab process enters the period during which it is cheaper on a transistor-count basis but still more expensive on a die-area basis. During this period, another unvarying principle takes place, namely the fact that more transistors can always provide a benefit. Thus, during this period the various products undergo one or more microarchitecture changes. Each microarchitecture change is planned well in advance and incorporates everything R&D has been able to figure out they can do with a given transistor budget. By the (eventual) time yields allow producing the same die size for the same cost, the transistor budget approaches 2× what it was in the established microarchitectures of the previous process technology.

By this time, another new, yet smaller process technology is ready to begin low-volume production and the entire cycle repeats.

Following are excerpts from press releases and independent reports on each of the past several generations of fabrication processes.

0.35 micron :

The Pentium Processor 120 MHz is the first volume microprocessor

to be built using a 0.35 micron process technology [...]

Intel's move to volume microprocessor manufacturing on a

0.35 micron process technology is an industry first. It allows the

die size to be reduced to approximately one-half the size of Intel's

Pentium processors built on 0.6 micron process technology (75, 90, and

100 MHz) which was introduced just last year, or about one-fourth the

size of the original Pentium processors built on the 0.8 micron

technology (60 and 66 MHz) introduced in 1993.

Intel's 0.35 micron process technology is a 3.3 volt BiCMOS

process that combines the energy-saving features of CMOS technology

and the high-performance characteristics of bi-polar technology. The

process features four layers of metal and full use of planarization

(polishing each surface of the wafer flat before building the next

layer upon it), and is built on 8-inch (200mm) wafers.

— Intel press release[8], 1995 Mar 27

0.25 micron :

The new 200- and 233-MHz mobile Pentium

processors with MMX technology are the first products manufactured

using Intel's advanced 0.25 micron process technology.

[...] The impressive increase in performance and decrease in power

consumption of 200- and 233-MHz mobile Pentium processors with MMX

technology are attributed primarily to the benefits of Intel's new

0.25 micron manufacturing technology. The 0.25 micron manufacturing

process and Intel's Voltage Reduction Technology decrease the core

voltage from 2.45 volts to 1.8 volts and the I/O interface from 3.3

volts to 2.5 volts relative to previous generation processors. This

reduction in voltages is a key element in enabling the production of

faster processors that consume less power.

— Intel press release[9], 1997 Sep 8

0.18 micron :

The mobile Pentium II processor at 400 MHz is Intel's first

processor built using Intel's 0.18 micron manufacturing process.

[...] The 0.18 micron manufacturing process allows the processor to

become smaller, faster and more powerful than its 0.25 micron

predecessors.

Intel's 0.18 micron process technology features

industry-leading transistor performance using transistor gate

lengths as small as 0.14 microns, a 2 nanometer (20 angstrom) gate

oxide thickness and a CoSi2 (cobalt silicide) layer for low

resistance. Interconnects feature six layers of aluminum and a low

capacitance SiOF insulator for high performance. [...]

— Intel press release[11], 1999 Jun 14

[...] The good news is that the transition from 0.25-micron to

0.18-micron is going very smoothly. Part of the reason for this is

because Intel started the transition to 0.18-micron very early on. On

June 14, 1999, Intel released their first 0.18-micron CPU, the mobile

Pentium II 400.

— AnandTech[12], 1999 Oct 25

Intel is the first company in

the industry to begin high-volume manufacturing utilizing 0.18-micron

process technology. Intel is using this technology in four factories

around the world. The 0.18-micron process technology features

structures that are smaller than 1/500th the thickness of a human

hair, smaller than bacteria and smaller than the visible wavelength of

light (for the human eye). The smallest structures on this new process

are as small as 0.13-microns. Intel's new 0.18-micron process

technology uses six layers of aluminum metal interconnect, a low SiOF

(fluorine-doped silicon dioxide) capacitance interconnect insulator,

and can feature voltages as low as 1.1 to 1.65 volts (the lowest

voltage of the products introduced today is 1.35 volts).

— Intel press release[13], 1999 Oct 25

0.13 micron (130 nm) :

Intel Corporation today announced five new processors based on

Intel's advanced 0.13-micron (130 nanometer) process technology [...]

are available in volume today at speeds up to 1.13 GHz, the

industry's fastest speed for mobile processors.

By incorporating its advanced 130-nanometer process technology,

Intel is able to build transistors (the switches used to create the

ones and zeroes of the information age) that are the fastest in the

industry. This new process technology also features high speed copper

interconnects that accelerate the flow of data inside the processor,

further increasing performance while consuming less power.

Processors built on Intel's 130-nanometer technology

consume up to 40 percent less power and are up to 20 percent faster

than the previous 180 (0.18-micron) nanometer process. Chips using

Intel's 130-nanometer technology contain circuitry that is about

1/1000th the width of a human hair (1000 nanometers equal 1-micron).

— Intel press release[17], 2001 Jul 30

90 nm :

Intel's first 90nm processor is here and after delays and much

waiting, we're getting much more than we bargained for. If you

thought this chip was just a larger cache on a smaller process you

were dead wrong...

AnandTech[18], 2002 Feb 1

Intel's 90 nm (a nanometer is one-billionth of a meter) process

technology is the most advanced semiconductor manufacturing process in

the industry, built exclusively on 300 mm wafers. This new process

combines high performance, low-power transistors, strained silicon,

high-speed copper interconnects and a new low-k dielectric material.

This is the first time all of these technologies have been integrated

into a single manufacturing process.

Intel® Pentium® 4 processors built on the 90-nm

process retain the multitasking capabilities of Hyper-Threading (HT)

Technology, and include new features such as enhanced Intel®

NetBurst® microarchitecture, a larger, 1 MB Level 2 (L2) cache and 13

new instructions.

— Intel press release[19], 2004 Feb 2

65 nm :

[The] all-new 65 nm Pentium Extreme Edition 955 based on Presler

[uses] on a state-of-the-art manufacturing process, comes with

double the L2 cache (2× 2 MB rather than 1× 1 MB), an accelerated

system clock speed (FSB1066 instead of FSB800) and a core clock speed

increase of approximately 8.25%. [It has] 376 million

transistors [on] two Cedar Mill type single core [dies].

[benchmark tests and results were here]

Intel's business has been going well. However, its

reputation suffered considerably when it failed to realize in time

that the public would resist the literally hot 90 nm NetBurst

portfolio. [...] Intel is in a good position [with] its progress in

65 nm manufacturing. Not only do the smaller structures allow for

ramping up production volumes, but they also clearly help to

decrease heat dissipation and power consumption. [...] The latest

Extreme Edition processor underscores the premise that manufacturing

technology is what matters most in the processor business. 65 nm

enables Intel to make up for the flaws in its current 90 nm portfolio

and to deliver competitive products over the coming months.

— Tom's Hardware[21], 2005 Dec 28

45 nm :

Called the biggest transistor advancements in 40 years by Intel

Co-Founder Gordon Moore, the processors are the first to use Intel's

Hafnium-based high-k metal gate (Hi-k) formula for the hundreds of

millions of transistors inside these processors. These Intel®

CoreTM 2 Extreme and Xeon® processors are also the first to

be manufactured on the company's 45-nanometer (nm) manufacturing

process, further boosting performance and lowering power

consumption.

Combining these two advancements with new processor

features enables Intel to continue delivering faster and more

energy-efficient processors that are better for the environment. The

breakthroughs clear the path for Intel to design products that are

25 percent smaller than previous versions and, thus, more

cost-effective, as well as the ability next year to pursue new ultra

mobile and consumer electronics "system on chip" opportunities.

— Intel press release[27], 2007 Nov 11

32 nm :

The introduction of new Intel® CoreTM i7, i5 and i3 chips

coincides with the arrival of Intel's groundbreaking new 32

nanometer (nm) manufacturing process — which for the first time in

the company's history — will be used to immediately produce and

deliver processors and features at a variety of price points, and

integrate high-definition graphics inside the processor. This

unprecedented ramp and innovation reflects Intel's $7 billion

investment announced early last year in the midst of a major global

economic recession.

Intel is unveiling several platform products, including

more than 25 processors, wireless adapters and chipsets, including

new Intel Core i7, i5 and i3 processors, [all] manufactured on the

company's 32nm process, which includes Intel's second-generation

high-k metal gate transistors. This technique, along with other

advances, helps increase a computer's speed while decreasing energy

consumption.

New Intel Core i7 and Core i5 processors also feature

exclusive Intel Turbo Boost Technology for adaptive performance, [and]

Intel® Hyper-Threading Technology, available in Intel Core i7,

Core i5 and Core i3 processors [...]

— Intel press release[66], 2010 Jan 7

22 nm :

Intel Corporation today introduced the quad-core 3rd generation

Intel® CoreTM processor family, delivering dramatic visual and

performance computing gains for gamers, media enthusiasts and

mainstream users alike. Available now in powerful, high-end desktop,

laptop and sleek all-in-one (AIO) designs, the new processors are the

first chips in the world made using Intel's 22-nanometer (nm) 3-D

tri-Gate transistor technology.

The combination of Intel's cutting-edge 3-D tri-gate transistor

technology and architectural enhancements help make possible up to

double the 3-D graphics and HD media processing performance compared

with Intel's previous generation of chips. As a result of the

stunning, built-in visual performance, all the things people love to

do on their PCs — from creating and editing videos and photos,

surfing the Web, watching HD movies or playing mainstream games — are

quicker, crisper and more life-like. With as much as 20 percent

microprocessor performance improvements and new technologies to speed

the flow of data to and from the chips, the new processors further

extend Intel's overall performance leadership.

In the coming months, additional versions of the 3rd

generation Intel Core processors will be available to power a new

wave of systems ranging from UltrabookTM devices, to servers and

intelligent systems in retail, healthcare and other industries. [...]

— Intel press release[98], 2012 Apr 23

Microarchitecture Innovations

Earlier microarchitectures added: pipeline, cache, floating-point unit, 2X or faster internal bus.

The P5 (original Pentium) microarchitecture implements the following improvements over the 80486:

- More efficient microcode control of pipeline for block copy and some other instructions

- Superscalar execution (ability to run two instructions through separate pipelines provided they don't interfere with each other)

- Faster math (e.g. full hardware multiply for integer and floating-point)

- More capable address calculation unit

- Less latency handling virtual 8086 mode

- Separate level 1 data and instruction caches

- 64-bit external data bus (twice that of the 80486)

- Adds MMX instructions (an integer-only 64-bit vector unit)

- Doubles the level 1 cache sizes

- Adds speculative execution and out-of-order completion

- Increases pipeline stages from 5 to 14

- Uses register renaming to make pipeline more efficient

- Has dedicated cache (256K or 512K, later 1M) on separate die(s) inside the CPU package, for higher speed (as compared to the previous third-party cache solutions)

- Uses dual independent buses (both 64 bit) to access cache and main memory simultaneously

- Decreases pipeline from 14 stages to 10

- Adds 256K level 2 cache on the same die

- Increases pipeline stages to 20

- Uses double-speed ALUs

- Adds an execution trace cache to reduce need to decode micro-ops

- (Starting with 3.06 GHz) Adds hyperthreading (two program counters and two copies of all user registers, with larger reorder buffer and reservation station to support dispatching two unrelated instruction streams at once)

- Increases the L2 cache size

- Adds the SSE2 instructions

- Has a 12-14 pipeline stages (less than Netborst but still more than Pentium III)

- Branch predictor now has global history

- Micro-ops fusion for more efficient handling of certain complex x86 instructions

- Adds the SSE3 instructions

- Expands cache interface to allow 2 cores to access a single L2 cache (the cache is "shared" or "unified")

- Decreases pipeline to 12 stages (always)

- Adds 64-bit instructions and more user registers (x86-64 extensions)

- Adds two pipeline stages (from 12-stage to 14-stage) to allow significantly higher clock rates

- Adds capacity throughout the pipeline: more instruction decoding, reorder, issue and scheduler capacity

- Increases FP units from 1 FMUL/FADD to 1 each FMUL, FADD, FLOAD and FSTORE

- Increases SSE units from 1 to 3

- Adds one integer ALU

- Has a larger L2 cache (increased from 2M in Yonah Core Duo to 4M in Merom Core 2 Duo)

The Nehalem microarchitecture:

- Has more efficient macrofusion, loop stream detecting and branch prediction [49]

- Brings back hyperthreading (larger reorder buffer and reservation station, twice as many user registers, etc)

- Puts all cores on a single die (as compared to Core 2 Quad)

- Adds Turbo Boost, which increases the clock speed of those cores that are being used whenever one or more cores is idle.

- Switches to a three-level cache design (256K L2 cache private to each core and large shared L3 cache; formerly one large L2 cache shared by each pair of cores — but all L2 content is mirrored in the L3 making coherency more efficient)

- Replaces FSB with direct memory interface and QPI for massively greater bandwidth

The Sandy Bridge microarchitecture:

- Adds a GPU on-die (primarily for mobile and low-end desktop segment)

- Doubles load/store capacity

- Doubles SIMD capacity (256-bit AVX instructions)

- Adds a ring bus interconnect between cores, cache, GPU and memory controller (similar to Beckton)

The Haswell microarchitecture:

- Improves branch predictor performance, "less wasted work" [102]

- Increases number of in-flight buffers throughout pipeline [102]

- Adds 2 FMA (fused multiply add) units and a second FP multiply unit

- Increases integer vector width to 256 bits (32 shorts or 16 ints) [104]

- Adds two ports (integer scalar and branch, store address) [102]

- Doubles L1 load/store bandwidth [106]

- Doubles L2 bandwidth and increases L2 TLB buffer size [106]

- Improves TLB and cache miss performance with speculative execution [102]

- Adds transactional memory instructions (makes mutex lock interactions much faster)[96]

- Adds S0ix "active idle" states (previously seen in Moorestown), continuous fine-grained power gating [106]

- For "ultrabook" (very low power mobile) market, Haswell includes the Platform Controller Hub in the package (a multi-chip module like Clarkdale/Arrandale) to save power[93]. All Haswell PCH's will be 32 nanometer.

- May support power-saving DDR3L and/or LPDDR3 memory[93]

- Server versions mayt support DDR4 through "experimental" (i.e. officially unsupported) configuration settings

- Offers more GPU shader cores, with fixed-function performance to match [103]

- Direct3D 11.1, OpenGL 3.2 [93]

- Can shut down half of the GPU for power savings (race-to-halt) [103]

- Improved performance of video codec and related functions [105]

- May include a 128M L4 cache on a separate die (rumor [97])

Skylake is the new microarchitecture for 14nm. It will support DDR4 (or an equivalent low-power variant) across all products. Improved GPGPU capability and/or a high-bandwidth interface to an enthusiast variant of Xeon Phi seem likely[95].

Skymont and Cannonlake are codenames I've found associated with 10nm, perhaps a die-shrink of Skylake.

Overview of Recent Intel Codenames

For the most part, each Intel microprocessor codename refers to a particular microarchitecture (design) on a particular process (lithography feature size). This table summarizes the codenames, by process (rows) and microarchitectures (columns):

| Brand: | Pentium 4 | Pent. 4 HT | (Pentium D) | Pentium M,

Core | Core 2 Duo | (Quad) | Core i5/i7 | 2nd and 3rd

Generation Core | (future) | (future) | |

| innovation: | hyperthreading | dual-core | power efficiency | unified cache | quad-core | SDRAM controller | integrated GPU | ||||

| process | |||||||||||

| 180 nm | Willamette

Nov 2000 | ||||||||||

| 130 nm | Northwood

Jan 2002 | Northwood HT

Nov 2002 | Banias | ||||||||

| 90 nm | Prescott

Feb 2004 | (Smithfield) | Dothan

May 2004 | ||||||||

| 65 nm | Cedar Mill | (Presler) | Yonah

Jan 2006 | Conroe

Aug 2006 | (Kentsfield) | ||||||

| 45 nm | Wolfdale

Jan 2008 | (Yorkfield) | Nehalem

Nov 2008 | ||||||||

| 32 nm | Westmere

Jan 2010 | Sandy Bridge

Jan 2011 | |||||||||

| 22 nm | Ivy Bridge

2Q 2012 | Haswell

2Q 2013? | |||||||||

| 14 nm? | Broadwell |

italics = "Tick", boldface = "Tock" in the Intel marketing department's "Tick-Tock" metaphor. Each "Tick" is below the preceding "Tock", and the subsequent "Tock" is to its right.

A "Tick" is the move to a smaller lithography, usually allowing for better power efficiency and sometimes added cache, or small feature enhancements that don't change the whole design (examples: a few new instuctions to speed encryption, or adding PCIe 3.0 to the integrated Northbridge functions).

According to Intel, their long-term goals in process technology development are to develop the next smaller size (fitting twice the transistors in the same area) every two years. When a new process is just starting to be productive, existing designs are the best designs to try to produce, because it is already well-known how those designs respond to irregularities in lithographic steps and because existing designs make for a smaller die size than any newer, upcoming designs.

A "Tock" is a new microarchitecture, allowing for better performance with (roughly) the same yield and transistor count, or for much better performance using a larger transistor count. Releasing a new microarchitecture only after the new lithography process has matured (i.e. during the year "in-between" Ticks) makes sense, and will naturally occur even if it is not planned that way, simply due to market forces and the allocation of limited development resources.

The "Tick-Tock" metaphor was first used by Intel marketing[23] in 2006, but the pattern can be easily seen to extend back before that time. Each "tick" has come near the beginning of an even-numbered year, and until Sandy Bridge each "tock" came near the end of the same year. (Thus the wait from a "tock" to the next "tick" is usually a bit longer).

Most of the codenames shown above are for the mainstream desktop variants, with the notable exception of Pentium M. Pentium M was the mobile version of Pentium III, marketed alongside the desktop processor Pentium 4. The difficulty in getting Pentium 4 to run on low power budget led to Pentium M continuing into the days of the Pentium 4 HT (with HyperThreading) and Pentium D (dual-core). The Pentium 4 and Pentium D microarchitecture design was abandoned when it became clear that the path towards the "terahertz transistor" was unsustainable due to heat dissipation, and the transition to "many" (4 or more) power-efficient cores in the desktop CPU was inevitable.

I have included two non-Tock columns that I consider significant: the Pentium D (first dual cores) and the Core 2 Quad (first quad cores). The Pentium D "Smithfield" was almost exactly two "Prescott" cores side by side on a die, linked to each other only through the shared front side bus that connects off-chip to the Northbridge. Similarly, a Core 2 Quad is little more than two Core 2 Duo dies in the same package, linked by the front side bus.

As of mid 2011, the 22nm lithography process seems to be on-track for production, but I anticipate that the "Haswell" developments might be delayed a bit if 22nm takes longer to reach yield maturity. In such a case, another codename (perhaps also ending in "bridge") might occupy a spot between Ivy Bridge and Haswell.

If 22nm successfully reaches high yields in large scale production, the next pocess technology will be 16nm, which Intel (as of their 2011 May 22 nanometer press event) is still calling "14nm".

Brief Chronology of Intel Silicon Fabrication Process Technology

| year | process | nominal feature length | wafer size | speed | product | transistors |

| 1971 | "p234" | 10 µM | 50 mm | 740 KHz | 4004 | 2250 |

| 1974 | "p338" | 6 µM | 75 mm | 2.0 MHz | 8080 | 6000 |

| 1976 | "p442" | 3 µM | 100 mm | 5.0 MHz | 8085 | 6500 |

| 1978 | 3 µM | 100 mm | 5.0 MHz | 8086 | 29,000 | |

| 1982 | "p546" | 1.5 µM | 125 mm | 6.0 MHz | 80286 | 134,000 |

| 1985 | P646 | 1.5 µM | 150 mm | 16 MHz | 80386 | 275,000 |

| 1989 | P648 | 1.0 µM | 150 mm | 25 MHz | 80486 | 1,180,000 |

| 1993 | P650 | 0.8 µM | 150 mm | 66 MHz | Pentium P5 | 3.1 million |

| 1994 | P852 | 0.6 µM | 200 mm | 100 MHz | Pentium P54C | 3.3 million |

| 1994 | 0.5 µM | 200 mm | 100 MHz | Pentium P54C | 3.3 million | |

| 1995 | P854 | 0.35 µM | 200 mm | 120 MHz | Pentium Pro | 5.5 million |

| 1997 | P856 | 0.25 µM | 200 mm | 233 MHz | Pentium II Deschutes | 9.5 million? |

| 1999 | P858 | 0.18 µM | 200 mm | 500 MHz | Pentium III Coppermine | 29 million |

| 2001 | P860

P1260 | 130 nm | 200 mm

300 mm | 1133 MHz | Pentium III Tualatin | 29 million |

| 2004 | P1262 | 90 nm | 300 mm | 2.8 GHz | Pentium 4 Prescott | 125 million |

| 2006 | P1264 | 65 nm | 300 mm | 2.17 GHz | Core Duo T2600 | 151 million |

| 2008 | P1266 | 45 nm | 300 mm | 2.67 GHz | Core 2 Duo E8200 | 410 million |

| 2010 | P1268 | 32 nm | 300 mm | 2.93 GHz | Core i3-530 | 382 million |

| 2012 | P1270 | 22 nm | 300 mm | ~ 3.1 GHz | Core i7-3720QM | 1.4 billion |

| 2014? | P1272 | 14 nm | 300 mm | ~ 3.3 GHz | (Broadwell) | ~ 2.5 billion? |

| 2017? | P1274

P1874(?) | 10 nm | 300 mm

450 mm | ~ 3.3 GHz | (Skymont) | ~ 5 billion? |

Sources: Wikipedia Transistor count, Pentium (and other similar articles, see the Wikipedia references below), and some of the sources listed under the lithography table

Actual Transistor Densities

This chart shows the variation between nominal transistor density (as expressed by a technology name like "0.13 micron" or "32 nanometer") and the actual density of transistors in CPU products over the entire history of the microprocessor.

Based on the size of a chip and the number of transistors (both are usually well-known, see list of sources after the table) the density in transistors per square millimeter is computed by the formula:

density = transistors / area

The area per transistor (APT, in square nanometers) is computed as:

APT = area / transistors

Then the effective process size (EPS, in nanometers) can be computed by either of the following formulas:

EPS = K1 / √density

EPS = K2 √APT

The constant K1 or K2 is adjusted so that the effective process size, on average, corresponds to the official process size. Currently K1 is about 82000 and K2 is about 12.3. The product K1K2 is 1000000, which is the number of nanometers in a millimeter.

| release date | name | nominal process size | transistors | die size | transistor density | APT | effective process size | source; alias(es); other notes | |||

| 19710000 | Intel 4004 | 10000 | 2300 | 13 mm2 | 176.92 | (75181 nm)2 | 6145. | 108 KHz clock | |||

| 19720000 | Intel 8008 | 10000 | 3500 | 15 mm2 | 233.33 | (65465 nm)2 | 5351. | 250 KHz clock | |||

| 19740000 | Intel 8080 | 6000 | 6000 | 20 mm2 | 300.00 | (57735 nm)2 | 4719. | 2.0 MHz clock | |||

| 19740000 | RCA 1802 | 5000 | 5000 | 27 mm2 | 185.19 | (73485 nm)2 | 6006. | ||||

| 19760000 | Intel 8085 | 3000 | 6500 | 20 mm2 | 325.00 | (55470 nm)2 | 4534. | ||||

| 19760000 | Zilog Z80 | 4000 | 8500 | 18 mm2 | 472.22 | (46018 nm)2 | 3761. | ||||

| 19780000 | Motorola 6809 | 5000 | 9000 | 21 mm2 | 428.57 | (48305 nm)2 | 3948. | ||||

| 19780000 | Intel 8086 | 3000 | 29000 | 29 mm2 | 1000.0 | (31623 nm)2 | 2584. | 5 to 10 MHz | |||

| 19790000 | Intel 8088 | 3000 | 29000 | 29 mm2 | 1000.0 | (31623 nm)2 | 2584. | ||||

| 19790000 | Motorola 68000 | 4000 | 68000 | 44 mm2 | 1545.5 | (25437 nm)2 | 2079. | ||||

| 19820000 | Intel 80286 | 1500 | 134000 | 69 mm2 | 1942.0 | (22692 nm)2 | 1854. | 6 to 12 MHz | |||

| 19851017 | Intel 80386DX-16 | 1500 | 275000 | 104 mm2 | 2644.2 | (19447 nm)2 | 1589. | ||||

| 19890410 | Intel 80386DX-33 | 1000 | 275000 | 39 mm2 | 7051.3 | (11909 nm)2 | 973.4 | ||||

| 19900507 | Intel 80486DX-33 | 1000 | 1180000 | 163 mm2 | 7239.3 | (11753 nm)2 | 960.7 | ||||

| 19930122 | Pentium 60MHz | 800 | 3100000 | 294 mm2 | 10540 | (9739 nm)2 | 796.0 | Original P5 | |||

| 19941010 | Pentium 75 | 600 | 3300000 | 163 mm2 | 20250 | (7028 nm)2 | 574.4 | P54C | |||

| 19950300 | Pentium 120 | 350 | 3300000 | 163 mm2 | 20250 | (7028 nm)2 | 574.4 | P54CQS: smaller transistors but same die dize: wasted space on die due to packaging constraints | |||

| 19950601 | Pentium 133 | 350 | 3300000 | 90 mm2 | 36670 | (5222 nm)2 | 426.8 | P54CS | |||

| 19951101 | Pentium Pro 150 | 500 | 5500000 | 306 mm2 | 17970 | (7459 nm)2 | 609.7 | ||||

| 19960300 | AMD K5 | 500 | 4300000 | 271 mm2 | 15870 | (7939 nm)2 | 648.9 | ||||

| 19970108 | Pentium MMX 166 | 280 | 4500000 | 128 mm2 | 35160 | (5333 nm)2 | 435.9 | ||||

| 19970300 | Pentium Overdriv 150 | 280 | 4500000 | 140 mm2 | 32140 | (5578 nm)2 | 455.9 | die size uncertain | |||

| 19970507 | Pentium II 233 | 350 | 7500000 | 203 mm2 | 36950 | (5203 nm)2 | 425.2 | "Klamath" | |||

| 19980824 | Pentium II 266A | 250 | 7500000 | 113 mm2 | 66370 | (3882 nm)2 | 317.2 | "Deschutes" | |||

| 19980800 | Celeron 300A | 250 | 19000000 | 154 mm2 | 123400 | (2847 nm)2 | 232.7 | SL2WM "Mendocino" (128K cache on-die) | |||

| 19990226 | Pentium III 450 | 250 | 9500000 | 128 mm2 | 74220 | (3671 nm)2 | 300.0 | "Katmai" (512K cache on separate chips) | |||

| 19991025 | Pentium III 500E | 180 | 28000000 | 106 mm2 | 264200 | (1946 nm)2 | 159.0 | "Coppermine" (256K cache on-die) | |||

| 20001100 | Pentium 4 1.3 | 180 | 42000000 | 217 mm2 | 193500 | (2273 nm)2 | 185.7 | SL5FW "Willamette", socket 423 | |||

| 20010400 | Pentium 4 1.7 | 180 | 42000000 | 217 mm2 | 193500 | (2273 nm)2 | 185.7 | SL67A "Willamette", socket 478 | |||

| 20010600 | Pentium III-S 1000 | 130 | 44000000 | 80 mm2 | 550000 | (1348 nm)2 | 110.2 | "Tualatin" with 512K cache on-die | |||

| 20020100 | Pentium 4 1.6A | 130 | 55000000 | 131 mm2 | 419800 | (1543 nm)2 | 126.1 | SL668 "Northwood A" | |||

| 20020708 | Itanium 2 1000 | 180 | 221000000 | 421 mm2 | 524900 | (1380 nm)2 | 112.8 | McKinley | |||

| 20030600 | Itanium 2 1400 | 130 | 410000000 | 374 mm2 | 1096000 | (955 nm)2 | 78.06 | SL6XE "Madison" (6M cache) | |||

| 20031103 | Pentium 4 EE 3.2 | 130 | 169000000 | 237 mm2 | 713100 | (1184 nm)2 | 96.79 | "Gallatin" | |||

| 20040300 | Pentium 4 505 | 90 | 125000000 | 112 mm2 | 1116000 | (947 nm)2 | 77.37 | SL7YU "Prescott", socket 478 | |||

| 20040510 | Pentium M 735 | 90 | 144000000 | 87 mm2 | 1655000 | (777 nm)2 | 63.53 | SL7EP "Dothan" (2M cache) | |||

| 20041108 | Itanium 2 1600 | 130 | 592000000 | 432 mm2 | 1370000 | (854 nm)2 | 69.82 | Madison 9M | |||

| 20050220 | Pentium 4 630 | 90 | 169000000 | 135 mm2 | 1252000 | (894 nm)2 | 73.05 | SL8Q7 "Prescott 2M", LGA 775 | |||

| 20050501 | Pentium D 840 XE | 90 | 230000000 | 206 mm2 | 1117000 | (946 nm)2 | 77.35 | SL88R "Smithfield" | |||

| 20060100 | Pentium D 631 | 65 | 188000000 | 81 mm2 | 2321000 | (656 nm)2 | 53.65 | SL9KG one "Cedar Mill" core (2M cache) | |||

| 20060600 | Pentium D 965 XE | 65 | 376000000 | 162 mm2 | 2321000 | (656 nm)2 | 53.65 | SL9AN "Presler" (two Cedar Mill cores) | |||

| 20060718 | Itanium 2 9050 | 90 | 1720000000 | 596 mm2 | 2886000 | (589 nm)2 | 48.11 | SL9PG Montecito | |||

| 20070107 | Core 2 Quad Q6600 | 65 | 582000000 | 286 mm2 | 2035000 | (701 nm)2 | 57.30 | SLACR "Kentsfield" (two Conroe dies each with 4M cache) | |||

| 20070121 | Core 2 Duo E4300 | 65 | 167000000 | 111 mm2 | 1505000 | (815 nm)2 | 66.64 | SLA99 "Allendale" (2M cache) | |||

| 20070422 | Core 2 Duo E6320 | 65 | 291000000 | 143 mm2 | 2035000 | (701 nm)2 | 57.30 | SLA4U "Conroe" (4M cache) | |||

| 20070608 | IBM POWER6 | 65 | 789000000 | 341 mm2 | 2314000 | (657 nm)2 | 53.73 | 8M of cache on-die | |||

| 20071111 | Xeon X5450 | 45 | 820000000 | 214 mm2 | 3832000 | (511 nm)2 | 41.75 | SLBBE "Harpertown" | |||

| 20080106 | Core 2 Duo E8400 | 45 | 410000000 | 107 mm2 | 3832000 | (511 nm)2 | 41.75 | SLB9J "Wolfdale" (6M cache) | |||